# Automotive control units for powertrain and active safety

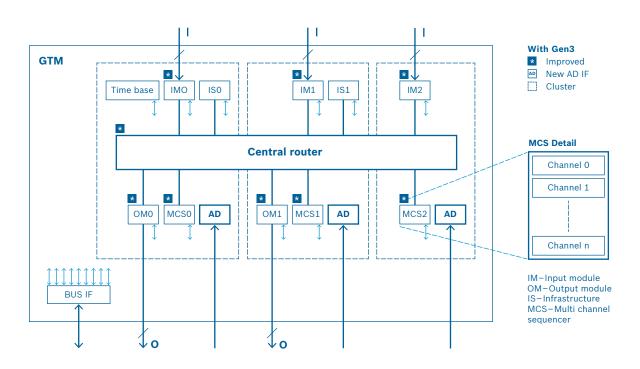

Generic Timer IP module (GTM)

#### **PRODUCT BENEFITS**

- ► Enables real-time control loops

- ➤ Deterministic multi-threaded architecture (8 threads per RISC unit)

- ► Programmability (special purpose RISC/ALU)

- ► Scalable and configurable architecture

- ► Easy integration due to generic interfaces and hierarchical architecture

- SystemC model support for in-system verification and early software development

- ► Supports model-based development

## 5 ns

input and output resolution for high-precision data capturing and data signal generation

#### TASK

The Generic Timer IP module (GTM) ensures accurate multi-input data acquisition and multi-output signal generation in automotive powertrain and active safety applications or in industrial closed-loop applications.

#### **FUNCTION**

Digital input signal changes are captured in real-time by the GTM and used together with digitized analog signals for computation. The powerful programmability by high level language (C) allows to generate virtually any output signal shapes with complex pulsewidth modulation (PWM). Multiple programming channels can act in parallel while still ensuring synchronous signal generation.

#### **VARIANTS**

Due to the modular design of the GTM a multiplicity of configurations are possible. These configurations are adjustable to the requirements of the customers.

### up to

### 1,500 MIPS

@ 200 Mhz clock frequency for high data processing speed and precise process control

#### TECHNICAL CHARACTERISTICS

| PWM generators*     | up to 192<br>resolution > 12 bit at any<br>frequency                                                                                                                                                                                        |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Outputs*            | up to 96<br>24 bit resolution (included<br>in 192 PWM generators)                                                                                                                                                                           |

| Programmable cores* | up to 10 (with up to 8 channels<br>each), working fully in parallel<br>with no CPU load                                                                                                                                                     |

| Inputs*             | up to 64<br>digital 24 bit filter for every input                                                                                                                                                                                           |

| Deliverables        | VHDL source code, test environment (test bench and integration tests), SystemC executable model for in-system verification and early software development, documentation, application notes, serial communication protocol software drivers |

<sup>\*</sup> larger configurations upon request